Programme Officiel

Contenus | Capacités attendues | Commentaires |

|---|---|---|

Modèle d’architecture séquentielle (von Neumann) | Dérouler l’exécution d’une séquence d’instructions simples du type langage machine. | Des activités débranchées sont proposées. |

Maintenant que nous avons vu quelle était la structure générale d'un ordinateur, nous allons nous intéresser plus précisément au rôle du processeur et de la mémoire(vive), et voir comment peuvent être dictées les instructions à l'unité de contrôle du processeur.

Communication entre le processeur et la mémoire

La mémoire contient plusieurs milliards de circuits mémoires un bit, qui sont organisés en cases mémoires de huit, seize, trente-deux, soixante-quatre bits. Chaque case a une adresse unique, leur nombre détermine la capacité de la mémoire vive de l'ordinateur.

Le processeur ne possède qu'un très petit nombre de cases mémoires très rapides appelées des registres dont la capacité dépasse rarement quelques dizaines d'octet pour des raisons de coût et de place. Source Wikipedia

Ces registres peuvent stocker des données et des adresses de la mémoire.

Le processeur est composé de transistors assemblés de façon à lui permettre de réaliser un petit nombre d'opérations simples, mais à réaliser ces opérations très rapidement.

Par exemple pour échanger des données avec la mémoire, le processeur utilise deux instructions permettant de:

- Transférer l'état d'un registre dans une case mémoire: le Stockage (STORE);

- transférer l'état d'une case mémoire dans un registre: le Chargement(LOAD).

Jeu d'instructions simplifié du processeur

Nous allons étudier un processeur simplifié avec deux registres disposant d'un jeu d'instructions restreints:

- STX x: stocke l'état du registre X dans la case mémoire d'adresse x.

- LDX x: charge l'état de la case mémoire d'adresse x dans le registre X.

- ADD X: additionne le contenu des registres et le stocke dans le registre X.

- DEC X: décrémente la valeur contenue dans le registre X, c'est à dire soustrait 1.

Écrire des suites d'instructions pour le processeur

- Supposons que notre mémoire contienne quatre valeurs 2, 3, 5, 7 dans les cases mémoires d'adresse 1, 2, 3, 4. Écrire la suite d'instructions qui permettra d'additionner ces quatre nombres et de stocker le résultat de cette addition dans la case mémoire 5.

- Écrire une séquence d’instructions qui multiplie par 3 le nombre contenu dans la case mémoire d’adresse 5 et stocke le résultat dans la case mémoire d’adresse 6.

Langage machine

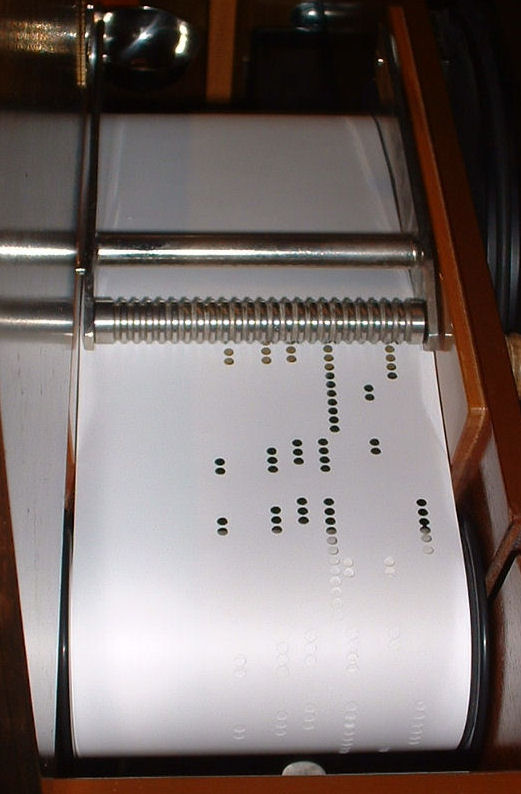

Dans les premières machines, les opérations à effectuer étaient écrites sur des bandes perforées qui en défilant indiquaient au processeur la suite d'opérations à réaliser.

"DrehorgelLochkarte". Licensed under Public Domain via Wikimedia Commons.

Puis cette idée a été abandonnée au profit d'une autre: celle d'enregistrer le programme dans la mémoire avec les données. Il convient alors de stocker les instructions du programme sous forme électrique dans la mémoire, on parle alors de langage machine.

Par exemple, on va utiliser le codage suivant pour les instructions:

instruction | codage | signification |

|---|---|---|

LDA | 0 | Charge l'état de la case mémoire donnée en argument dans le registre A. |

LDB | 1 | Charge l'état de la case mémoire donnée en argument dans le registre B. |

STA | 2 | Stocke l'état du registre A dans la case mémoire donnée en argument. |

STB | 3 | Stocke l'état du registre B dans la case mémoire donnée en argument. |

ADD | 4 | Additionne le contenu des registres et le stocke dans le registre donné en argument. |

DEC | 5 | Décrémente la valeur contenue dans le registre donné en argument, c'est à dire soustrait 1. |

En ce qui concerne les arguments des instructions:

- Les cases mémoires sont codées par leur adresse numérique,

- et les registres A et B sont codés par 0 et 1.

Si on désire additionner le contenu des valeurs contenues dans les cases mémoires 5 et 6, et les stocker dans la case mémoire 7, on réalise la suite d'instructions suivantes:

LDA 5,LDB 6,ADD A,STA 7soit:

0 5,1 6,4 0,2 7Il suffit maintenant d’ajouter au processeur un nouveau registre qui débute à 100, le compteur de programme ou PC (program counter), sur lequel on va stocker le programme à exécuter, et à chaque étape, le processeur :

- Charge le contenu des cases mémoires d’adresses PC et PC + 1,

- décode le premier de ces nombres en une instruction (0 devient LDA , 1 LDB , etc.),

- décode le deuxième de ces nombres comme un argument à l'instruction(p.ex: une adresse mémoire dans le cas des

LOAD), - exécute l’instruction en question,

- et ajoute 2 au registre PC pour passer à l'instruction suivante.

Écrire un programme en langage machine

- Traduire les suites d'instructions des applications de la partie précédente en langage machine.

- Écrire ces programmes en binaire avec des mots de 4 bits.

Vers des instructions plus évoluées

Si on désire réaliser des boucles et des tests, on ajoute trois instructions au processeur qui seront codées ainsi:

instruction | codage | signification |

|---|---|---|

JMP | 6 | Fait "sauter"(JUMP) le programme vers une ligne donnée en argument |

JMPZ | 7 | Comme JUMP, mais uniquement si le registre A est 0. |

END | 8 | Termine le programme |

Comment écrire une boucle?

et sont deux entiers positifs par exemple: 5 et 3.

Expliquer ce que fait ce programme et indiquer ce que contiennent les cases mémoires 10 et 11 en fin d'exécution.

adresse | valeur | signification |

|---|---|---|

… | … | |

10 | x | case mémoire |

11 | y | case mémoire |

… | ||

100 | 0 | LDA |

101 | 10 | case mémoire |

102 | 1 | LDB |

103 | 10 | case mémoire |

104 | 7 | JMPZ |

105 | 112 | 112 |

106 | 5 | DEC |

107 | 0 | A |

108 | 4 | ADD |

109 | 1 | B |

110 | 6 | JMP |

111 | 104 | 104 |

112 | 3 | STB |

113 | 11 | case mémoire |

114 | 8 | END |

… |

Comment écrire une instruction conditionnelle?

Pa exemple, on veut vérifier si deux valeurs sont égales:

- si oui stocker

079, la lettre «O» en ASCII dans la case mémoire10. - si oui stocker

078, la lettre «N» ASCII dans la case mémoire10.

et sont deux entiers positifs stockés initialement dans les cases mémoires 10 et 11.

adresse | valeur | signification |

|---|---|---|

… | … | |

10 | x | case mémoire |

11 | y | case mémoire |

12 | 78 | case mémoire |

13 | 79 | case mémoire |

… | ||

100 | 0 | LDA |

101 | 10 | x |

102 | 1 | LDB |

103 | 11 | y |

104 | 7 | JMPZ |

105 | 112 | 112 |

106 | 5 | DEC |

107 | 0 | A |

108 | 5 | DEC |

109 | 1 | B |

110 | 6 | JMP |

111 | 104 | 104 |

112 | 3 | STB |

113 | 11 | 11 |

114 | 0 | LDA |

115 | 11 | 11 |

116 | 7 | JMPZ |

117 | 122 | 122 |

118 | 0 | LDA |

119 | 12 | 78 |

120 | 6 | JMP |

121 | 124 | 124 |

122 | 0 | LDA |

123 | 13 | 79 |

124 | 2 | STA |

125 | 10 | 10 |

126 | 8 | END |

- Chapitre 15: L'organisation d'un ordinateur Informatique et sciences du numérique Spécialité ISN en terminale S - Avec des exercices corrigés et des idées de projets par Gilles Dowek